在高速數(shù)字電路和高速串行通信領(lǐng)域(如 PCIe, USB, DDR, HDMI, SATA 等),差分信號(hào)布線規(guī)則是保證信號(hào)完整性 (SI)、抑制電磁干擾 (EMI) 以及提升系統(tǒng)可靠性的核心技術(shù)基石。與傳統(tǒng)的單端信號(hào)相比,差分信號(hào)利用一對(duì)相位相反、幅度相等的信號(hào)線進(jìn)行傳輸,其固有的共模噪聲抑制能力、更強(qiáng)的抗干擾性以及更低的電磁輻射特性,使其成為高速數(shù)據(jù)傳輸?shù)氖走x方案。然而,差分信號(hào)的優(yōu)勢(shì)能否充分發(fā)揮,極度依賴于嚴(yán)謹(jǐn)、精確的 PCB 布線實(shí)踐。任何對(duì)差分對(duì)布線原則的疏忽,都可能導(dǎo)致信號(hào)質(zhì)量急劇惡化、時(shí)序混亂,甚至系統(tǒng)功能失效。

差分對(duì)布線的核心目標(biāo)在于維持這對(duì)信號(hào)線從源端到接收端全程的高度對(duì)稱性。這種對(duì)稱性體現(xiàn)在電氣特性(阻抗、延遲)和物理形態(tài)(長(zhǎng)度、間距、走線環(huán)境)等多個(gè)維度。理解并嚴(yán)格遵守其布線規(guī)則,是高速 PCB 設(shè)計(jì)工程師的必備技能。

? 規(guī)則:差分對(duì)內(nèi)的 P(正)線和 N(負(fù))線必須保持長(zhǎng)度相等,長(zhǎng)度偏差需嚴(yán)格控制在系統(tǒng)允許的范圍內(nèi)(通常為幾個(gè) mil 到幾十個(gè) mil,例如 5-10 mil 是常見(jiàn)的高要求目標(biāo))。

? 原理:信號(hào)在 PCB 走線上傳播存在延遲。如果 P 線和 N 線長(zhǎng)度不等,信號(hào)到達(dá)接收端的時(shí)間就會(huì)產(chǎn)生差異(稱為對(duì)內(nèi)偏差)。這會(huì)導(dǎo)致差分信號(hào)在接收端疊加時(shí),原本應(yīng)該抵消的共模分量無(wú)法完全抵消,有效差分電壓降低,信號(hào)質(zhì)量下降,嚴(yán)重時(shí)產(chǎn)生時(shí)序錯(cuò)誤。長(zhǎng)度偏差是導(dǎo)致差分信號(hào)相位失配的主要因素。

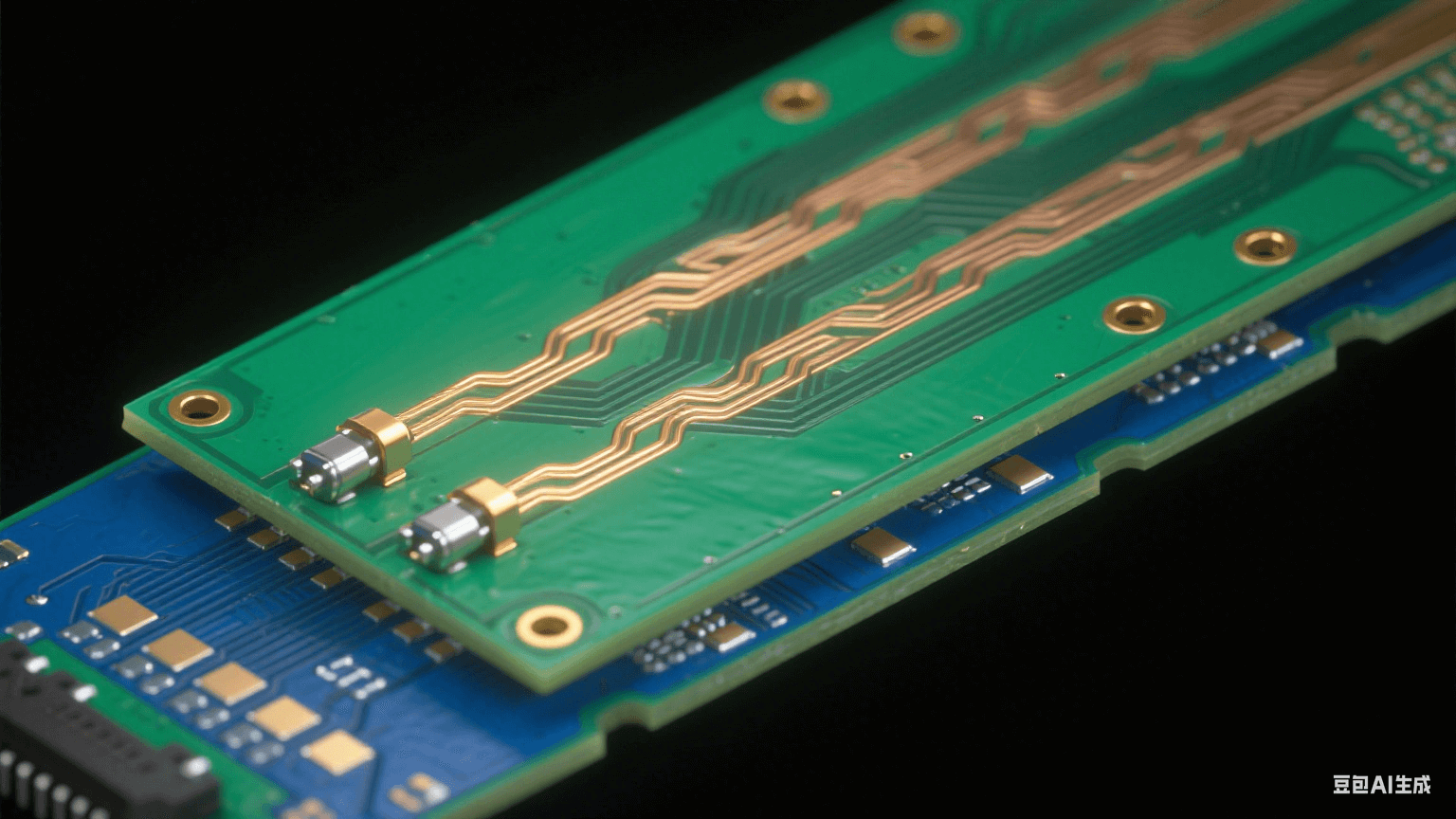

? 實(shí)現(xiàn):使用 PCB 設(shè)計(jì)軟件的差分對(duì)布線功能,并設(shè)置嚴(yán)格的對(duì)內(nèi)長(zhǎng)度容差規(guī)則。布線后通過(guò)蛇形線(Tuning / Meander)在較短的線上精確補(bǔ)償長(zhǎng)度。

? 規(guī)則:差分對(duì)必須設(shè)計(jì)并實(shí)現(xiàn)精確的差分阻抗(Zdiff,如 90Ω, 100Ω 等)和共模阻抗(Zcomm)。

? 原理:阻抗不連續(xù)會(huì)導(dǎo)致信號(hào)反射,破壞信號(hào)完整性。差分阻抗是信號(hào)在差分模式下看到的特征阻抗。共模阻抗影響共模噪聲的抑制能力。阻抗值由走線寬度(W)、走線間距(S)、介質(zhì)層厚度(H)、介電常數(shù)(Er)以及參考平面等因素決定。

? 實(shí)現(xiàn):

? 利用廠商提供的阻抗計(jì)算工具(如 Polar SI9000)或電磁場(chǎng)求解器進(jìn)行精確計(jì)算和仿真。

? 與 PCB 制造商緊密溝通,確認(rèn)其工藝能力(銅厚、介質(zhì)厚度 / Er 控制精度)。

? 在 PCB 設(shè)計(jì)規(guī)則中定義并約束差分對(duì)的線寬、線距以及到參考平面的距離。

? 避免在差分對(duì)路徑上出現(xiàn)可能導(dǎo)致阻抗突變的因素(如焊盤、過(guò)孔、參考平面缺口、靠近其他信號(hào)或器件)。

? 規(guī)則:P 線和 N 線在物理布局和走線環(huán)境上應(yīng)盡可能保持鏡像對(duì)稱。

? 原理:任何破壞對(duì)稱性的因素都會(huì)引入額外的對(duì)內(nèi)偏差,可能導(dǎo)致共模噪聲增加、EMI 加劇以及接收端信號(hào)質(zhì)量劣化。

? 實(shí)現(xiàn):

? 并行走線:P 線和 N 線應(yīng)始終緊密平行布線,間距(S)保持恒定。避免不必要的交叉或分離。

? 環(huán)境一致:確保 P 線和 N 線處于相同的疊層結(jié)構(gòu)中,具有相同的參考平面(最好是完整的地平面),并遠(yuǎn)離可能產(chǎn)生不對(duì)稱耦合的干擾源(如強(qiáng)電流、時(shí)鐘線)。

? 過(guò)孔對(duì)稱:如果需要換層,P 線和 N 線應(yīng)使用相同類型、相同數(shù)量的過(guò)孔,并且過(guò)孔的位置應(yīng)盡量對(duì)稱。差分過(guò)孔設(shè)計(jì)有助于維持阻抗連續(xù)性和對(duì)稱性。

? 器件布局對(duì)稱:驅(qū)動(dòng)器和接收器芯片的差分引腳布局應(yīng)便于對(duì)稱布線,避免強(qiáng)制繞行導(dǎo)致的不對(duì)稱。

? 規(guī)則:差分對(duì)下方(或上方)必須提供完整、無(wú)分割的參考平面(通常是地平面 GND,有時(shí)是電源平面 PWR)。

? 原理:參考平面是信號(hào)返回電流的主要路徑。不連續(xù)的參考平面(如平面上的開(kāi)槽、分割線、密集過(guò)孔區(qū)域)會(huì):

? 破壞差分阻抗和共模阻抗的連續(xù)性,引起反射。

? 增大環(huán)路面積,導(dǎo)致輻射 EMI 增加。

? 可能迫使返回電流繞遠(yuǎn)路,產(chǎn)生地彈噪聲并增加串?dāng)_。

? 實(shí)現(xiàn):

? 在差分對(duì)布線區(qū)域下方,保持地平面的完整性至關(guān)重要,避免在關(guān)鍵高速差分通道下方進(jìn)行平面分割。

? 如果必須跨越平面分割區(qū),應(yīng)在跨越點(diǎn)附近放置縫合電容(如 0.1uF),為高頻返回電流提供就近通路(效果有限,應(yīng)盡量避免)。

? 保持差分對(duì)與參考平面的距離(H)穩(wěn)定,避免使用厚芯材區(qū)域走高速差分線。

? 規(guī)則:盡量減少差分對(duì)上的過(guò)孔數(shù)量;必須使用時(shí),需優(yōu)化設(shè)計(jì)以最小化阻抗不連續(xù)和信號(hào)反射。

? 原理:過(guò)孔本質(zhì)上是三維結(jié)構(gòu),會(huì)引入寄生電容和電感,導(dǎo)致阻抗下降(容性不連續(xù))和信號(hào)反射。同時(shí),過(guò)孔殘樁(Stub)會(huì)引起嚴(yán)重的信號(hào)完整性問(wèn)題,尤其在高速率下。

? 實(shí)現(xiàn):

? 最少化過(guò)孔:優(yōu)化布局,盡量避免差分線換層。

? 優(yōu)化過(guò)孔設(shè)計(jì):

? 使用小尺寸過(guò)孔(減小寄生電容)。

? 在允許的情況下,移除非功能焊盤(Anti-pad)以減小電容。

? 增加過(guò)孔與周圍銅箔(平面)的間隙(Anti-pad 尺寸),以減小寄生電容。

? 采用背鉆(Back Drilling)技術(shù)去除過(guò)孔殘樁,這是處理高速長(zhǎng)鏈路(如背板)的關(guān)鍵工藝。

? 對(duì)稱打孔:P 線和 N 線的過(guò)孔位置、類型和數(shù)量必須嚴(yán)格對(duì)稱。

? 就近放置回流地過(guò)孔:在差分過(guò)孔附近放置接地過(guò)孔,為返回電流提供低阻抗路徑,有助于維持阻抗和減少 EMI。

? 規(guī)則:

? 對(duì)內(nèi)間距 (S):保持恒定,其值直接影響差分阻抗。

? 對(duì)外間距 (D):差分對(duì)與其他信號(hào)(單端或其他差分對(duì))、電源、器件、板邊等應(yīng)保持足夠大的距離。

? 原理:

? 對(duì)內(nèi)間距 (S) 的恒定是維持阻抗一致性和對(duì)稱性的基礎(chǔ)。

? 加大對(duì)外間距 (D) 的主要目的是:

? 減少串?dāng)_ (Crosstalk):防止其他信號(hào)干擾差分對(duì),或差分對(duì)的強(qiáng)信號(hào)干擾其他敏感電路(尤其是時(shí)鐘、復(fù)位、模擬信號(hào))。

? 降低 EMI:更大的間距有助于減小不同差分對(duì)之間的電磁耦合,降低整體輻射。

? 實(shí)現(xiàn):

? 在 PCB 設(shè)計(jì)規(guī)則中明確設(shè)定對(duì)內(nèi)間距 (S) 和最小對(duì)外間距 (D) 約束。

? 使用 3W(線中心間距≥3 倍線寬)或更嚴(yán)格的規(guī)則(如 5H,H 為到參考平面距離)來(lái)抑制串?dāng)_。對(duì)于非常高速或高密度設(shè)計(jì),可能需要借助仿真確定最佳間距。

? 避免差分對(duì)靠近板邊,以防輻射超標(biāo)。

? 規(guī)則:在差分傳輸線的接收端(有時(shí)也在發(fā)送端)實(shí)施適當(dāng)?shù)亩私与娮杵ヅ洹?/span>

? 原理:端接電阻的值(通常等于差分阻抗Zdiff)用于吸收傳輸線末端的信號(hào)能量,消除反射。這對(duì)于防止信號(hào)過(guò)沖、振鈴,確保接收端獲得干凈的眼圖至關(guān)重要。

? 實(shí)現(xiàn):

? 最常見(jiàn)方式:在接收器的差分輸入端并聯(lián)一個(gè)阻值等于 Zdiff 的電阻(如 100Ω),直接跨接在 P 和 N 線之間(差分端接)。

? 其他方式:根據(jù)具體協(xié)議和芯片要求,可能采用戴維南端接(分壓)、AC 端接(電容 + 電阻)等。務(wù)必參考芯片手冊(cè)和應(yīng)用筆記的要求。

? 布局要點(diǎn):端接電阻必須盡可能靠近接收器(或驅(qū)動(dòng)器)的引腳放置!走線要短且對(duì)稱,避免引入額外的阻抗不連續(xù)或延遲偏差。

? 規(guī)則:對(duì)于關(guān)鍵的高速差分鏈路,設(shè)計(jì)階段必須進(jìn)行信號(hào)完整性 (SI) 和電源完整性 (PI) 仿真,PCB 制作完成后必須進(jìn)行嚴(yán)格的測(cè)試驗(yàn)證。

? 原理:理論計(jì)算和規(guī)則約束是基礎(chǔ),但實(shí)際 PCB 的復(fù)雜性(疊層誤差、材料特性、制造公差、過(guò)孔效應(yīng)、串?dāng)_耦合等)需要通過(guò)仿真進(jìn)行預(yù)測(cè)和優(yōu)化。測(cè)試則是最終確認(rèn)設(shè)計(jì)是否達(dá)標(biāo)、制造是否合格的唯一手段。

? 實(shí)現(xiàn):

? 前仿真(Pre-layout):在布線前,基于目標(biāo)拓?fù)洹⑵骷P秃图s束規(guī)則進(jìn)行仿真,指導(dǎo)布局布線策略。

? 后仿真(Post-layout):提取實(shí)際布線的精確模型(如 S 參數(shù)模型),進(jìn)行時(shí)域(眼圖、TDR)和頻域仿真,評(píng)估信號(hào)質(zhì)量(抖動(dòng)、噪聲容限、時(shí)序裕量)、阻抗連續(xù)性和串?dāng)_水平。

? 測(cè)試驗(yàn)證:使用高速示波器(帶差分探頭)測(cè)量接收端眼圖、抖動(dòng);使用矢量網(wǎng)絡(luò)分析儀 (VNA) 測(cè)量差分阻抗和 S 參數(shù);進(jìn)行協(xié)議一致性測(cè)試和系統(tǒng)級(jí) EMC 測(cè)試。

? 高速 SerDes 接口:PCIe (Gen4/5/6 及更高)、USB (3.2/4)、以太網(wǎng) (10/25/40/100/400GbE)、SATA、SAS 等是差分信號(hào)布線規(guī)則應(yīng)用最密集的領(lǐng)域。速率越高(如 112Gbps PAM4),規(guī)則執(zhí)行越要嚴(yán)苛,對(duì)材料(Low-Dk/Df)、制造工藝(背鉆精度、蝕刻均勻性)和仿真深度要求也越高。

? 內(nèi)存接口:DDR4/DDR5 的時(shí)鐘 (CK/CK#)、數(shù)據(jù)選通 (DQS/DQS#) 和部分?jǐn)?shù)據(jù)線采用差分信號(hào),對(duì)等長(zhǎng)、阻抗和時(shí)序要求極高。

? 板級(jí)互連與背板:系統(tǒng)內(nèi)板卡間的高速連接通常依賴差分對(duì)(如 SFP+/QSFP + 光模塊接口、背板連接器),需處理更長(zhǎng)的距離、更多連接器和過(guò)孔,背鉆成為常用工藝。

? 高密度互連 (HDI) 設(shè)計(jì):在手機(jī)、可穿戴設(shè)備等空間受限場(chǎng)景,如何在極小空間內(nèi)滿足差分對(duì)布線規(guī)則(尤其是間距和對(duì)稱性)是巨大挑戰(zhàn),往往需要更精細(xì)的線寬 / 線距(3/3 mil 或更小)、微過(guò)孔和先進(jìn)疊層設(shè)計(jì)。

? 射頻與高速混合設(shè)計(jì):高速數(shù)字差分線與射頻模擬電路的共存需要更嚴(yán)格的隔離(間距、屏蔽)和地平面設(shè)計(jì),防止數(shù)字噪聲干擾敏感的射頻信號(hào)。

特性 | 單端信號(hào) | 差分信號(hào) | 優(yōu)勢(shì)對(duì)比 |

信號(hào)線數(shù)量 | 1 根信號(hào)線 + 公共返回路徑 (地) | 2 根信號(hào)線 (P 和 N) | 差分多占用 1 根線 |

抗干擾原理 | 依賴參考地電平 | 依靠 P 與 N 信號(hào)的差值 | 差分: 超強(qiáng)共模噪聲抑制能力 |

抗噪能力 | 較弱,易受地噪聲和串?dāng)_影響 | 極強(qiáng),外部共模干擾被大幅抑制 | 差分勝出 |

EMI 輻射 | 較高(電流環(huán)路面積較大) | 極低(磁場(chǎng)相互抵消,環(huán)路面積小) | 差分勝出,更易通過(guò) EMC 認(rèn)證 |

電壓擺幅 | 較大(需達(dá)到邏輯門限) | 較小(接收器檢測(cè)差值) | 差分: 功耗更低,開(kāi)關(guān)速度更快 |

時(shí)序精度 | 受噪聲和反射影響較大 | 更高(噪聲抵消,開(kāi)關(guān)點(diǎn)定義更清晰) | 差分勝出,適合高速時(shí)序 |

布線復(fù)雜度 | 相對(duì)簡(jiǎn)單 | 復(fù)雜(需嚴(yán)格對(duì)稱、等長(zhǎng)、阻抗控制) | 單端勝出,但高速領(lǐng)域差分是必需 |

典型應(yīng)用 | 低速控制信號(hào)、電源 | 高速串行鏈路 (PCIe, USB, DDR 時(shí)鐘等) | 差分是高速領(lǐng)域的絕對(duì)主流 |

參考平面依賴 | 強(qiáng)(返回路徑關(guān)鍵) | 較弱(但仍需保證對(duì)稱參考環(huán)境) | 差分: 對(duì)地彈噪聲敏感度略低 |

差分信號(hào)布線規(guī)則絕非紙上談兵的理論教條,而是無(wú)數(shù)次工程實(shí)踐與失敗教訓(xùn)凝結(jié)而成的設(shè)計(jì)鐵律。從精確的阻抗計(jì)算與等長(zhǎng)控制,到貫穿始終的對(duì)稱性原則、對(duì)參考平面完整性的執(zhí)著、對(duì)過(guò)孔效應(yīng)的謹(jǐn)慎處理、對(duì)間距的精細(xì)管理、正確的端接匹配,再到不可或缺的仿真與測(cè)試驗(yàn)證,每一個(gè)環(huán)節(jié)都緊密關(guān)聯(lián),共同構(gòu)筑起高速信號(hào)穩(wěn)定可靠傳輸?shù)臉蛄骸?/span>

隨著數(shù)據(jù)速率不斷攀升(112Gbps PAM4 已商用,224Gbps 在路上),信號(hào)完整性裕量被極度壓縮,對(duì)差分對(duì)布線的要求只會(huì)越來(lái)越苛刻。工程師必須深刻理解這些規(guī)則背后的電磁學(xué)原理,熟練運(yùn)用現(xiàn)代 EDA 工具進(jìn)行設(shè)計(jì)、約束管理和仿真分析,并與 PCB 制造商保持深度協(xié)作,確保設(shè)計(jì)意圖能精準(zhǔn)地轉(zhuǎn)化為實(shí)物。唯有將差分信號(hào)布線規(guī)則內(nèi)化為設(shè)計(jì)本能,才能在高速數(shù)字系統(tǒng)的復(fù)雜性與性能需求之間找到最優(yōu)解,打造出穩(wěn)定、高效、合規(guī)的電子產(chǎn)品。掌握并極致踐行差分信號(hào)布線規(guī)則,是駕馭高速數(shù)字時(shí)代洪流的必備船槳。